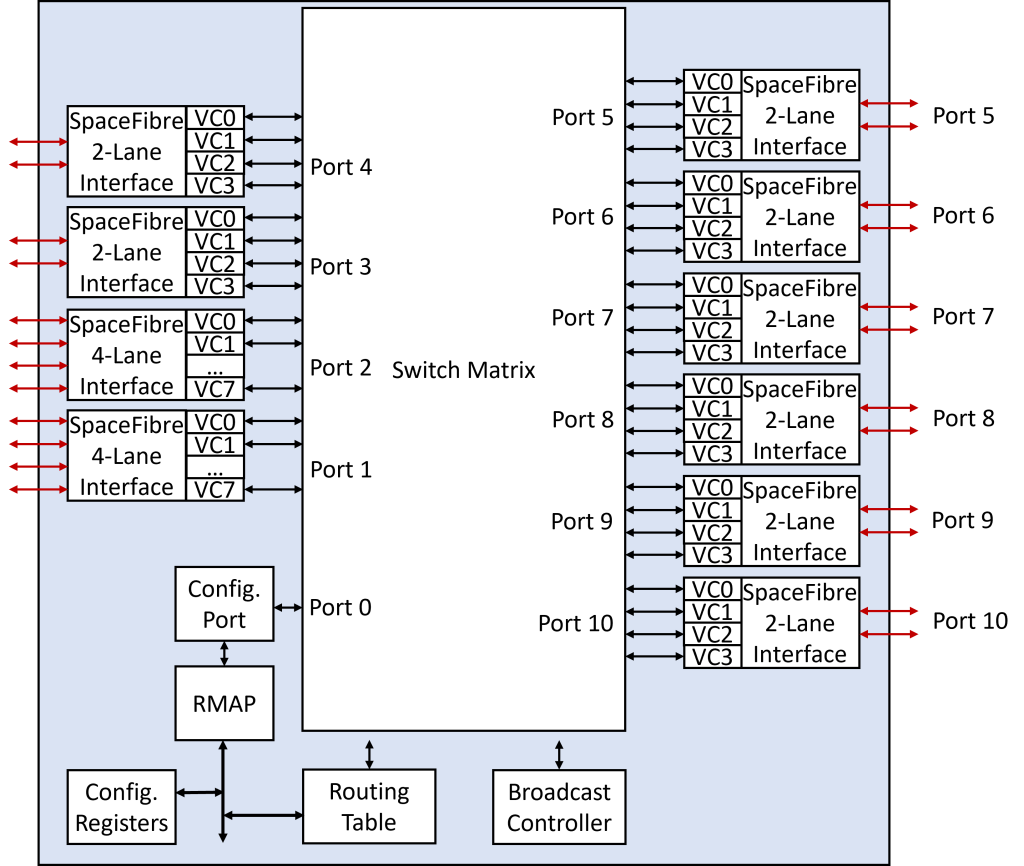

STAR-Tiger is a high-performance SpaceFibre routing switch. A block diagram of the SpaceFibre routing switch FPGA used in the STAR-Tiger SpaceFibre routing switch is shown in Figure 1. It is implemented using the STAR-Dundee SpaceFibre Multi-Lane Routing Switch IP Core and contains the following:

- A routing switch matrix with ten SpaceFibre ports and an internal configuration port.

- Two quad-lane SpaceFibre ports (ports 1-2) with eight virtual channels each.

- Eight dual-lane SpaceFibre ports (ports 3-10) with four virtual channels each.

- An RMAP configuration port (port 0) which accesses the SpaceFibre router configuration, control and status registers.

- A routing table which is configured over the configuration port and which determines the logical address to output port-number mapping.

- A broadcast controller which broadcasts broadcast-messages on each of the 256 possible broadcast channels. The broadcast controller also provides the time-slot timing for the schedule quality of service.

- Note: TMR is not implemented in the current STAR-Tiger FPGA design.

Figure 1: Block Diagram of Routing Switch FPGA

STAR-Tiger is capable of data rates up to 19 Gbit/s on its quad-lane ports and 9.6 Gbit/s on its dual-lane ports, with an aggregate throughput (all ports in both directions) of around 200 Gbit/s.